How to: Create basic bitstream and first stage bootloader for the ZedBoard SDK

Introduction

This guide will help the user to understand the methods that need to be done in order to create a basic bitstream and a first stage bootloader for the ZedBoard. Included in the RidgeRun SDK there are default files for this components, but this wiki will serve as a tutorial for creating new ones.

Steps

1. Make sure you have installed the Xilinx tools. For reference check the following:

Ubuntu 12.04 useful installation hints.

2. Open Xilinx Platform Studio:

xps

3. Select "Create new project using Base System Builder".

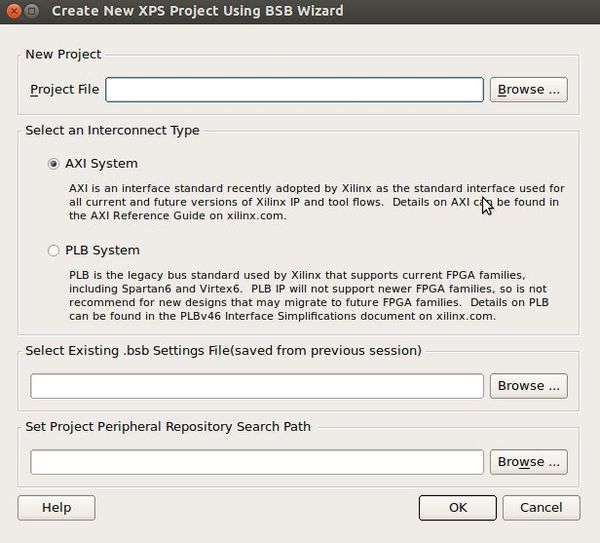

4. Select the project folder and the "AXI System Interconnect Type" as shown in the figure and click ok:

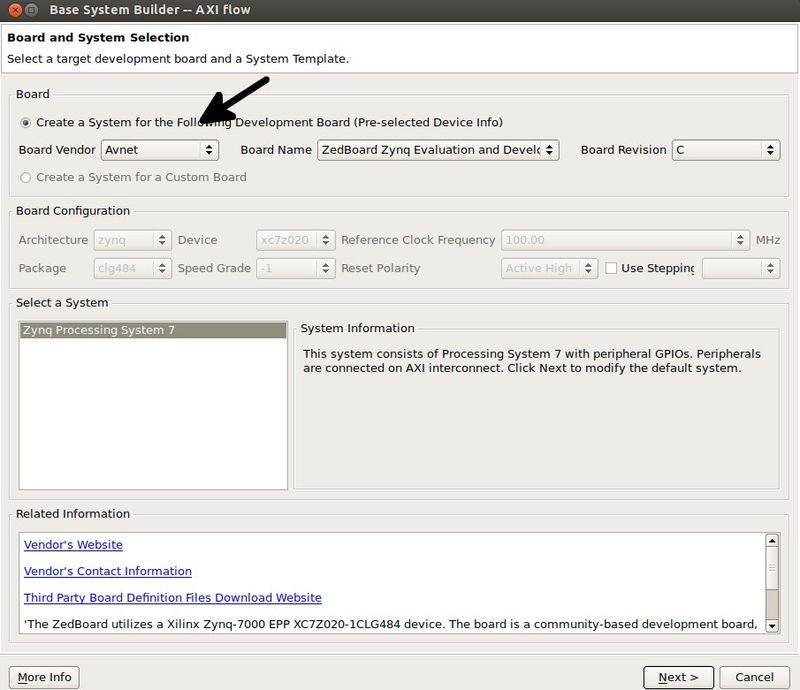

5. Select the "Avnet" vendor and the "ZedBoard" board, then click next:

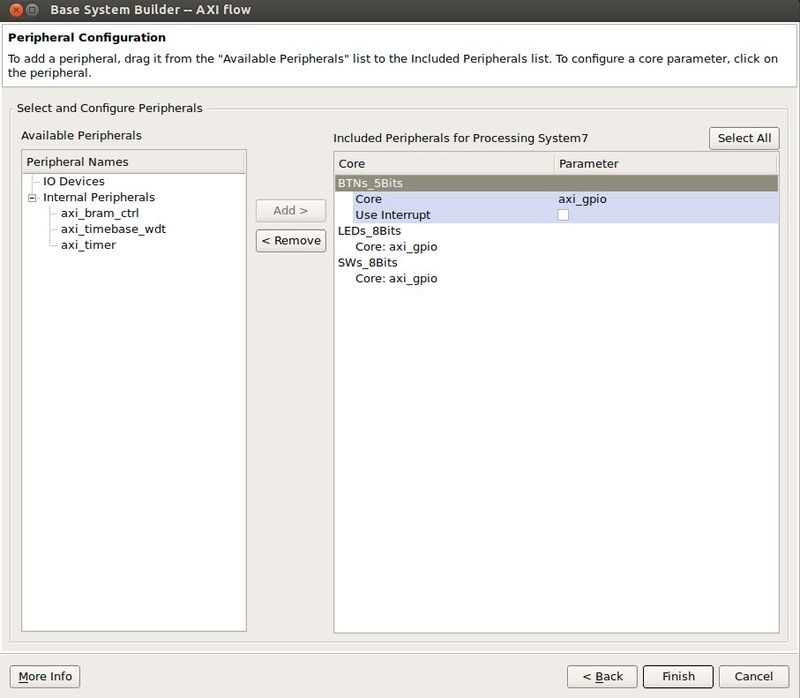

6. Leave the default peripheral configuration and click finish:

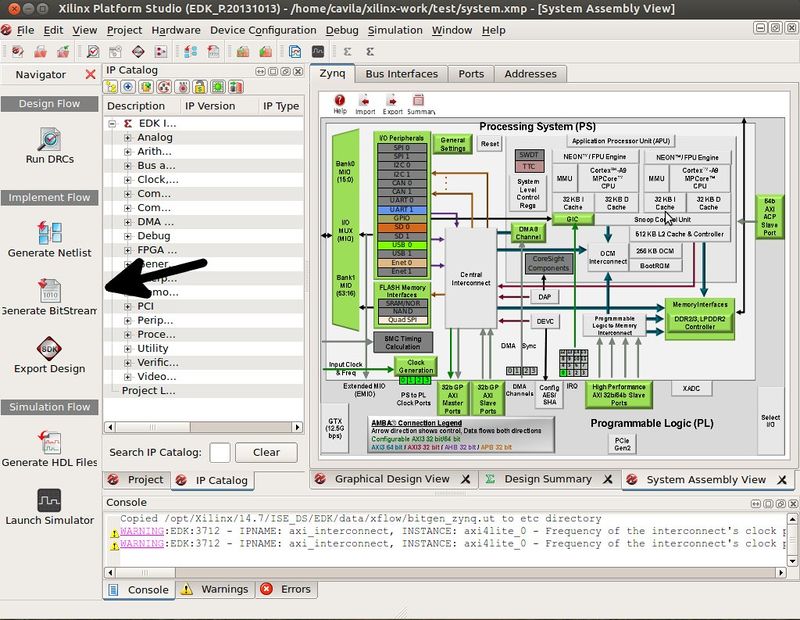

7. After this steps the project will be ready for bitstream generation. Select "Generate Bitstream" option. Once is complete select "Export Design" option, the one just below the previous one.

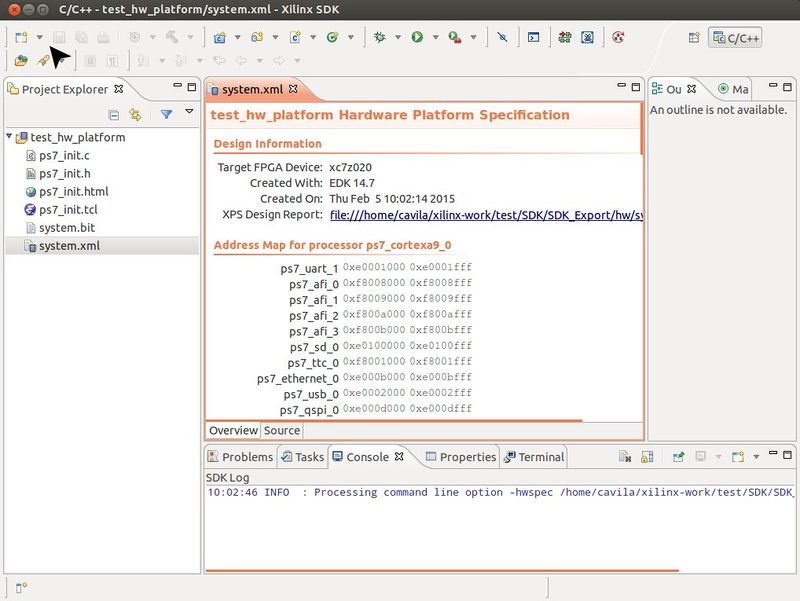

8. We will need to export this design to the Xilinx SDK to be able to generate the first stage bootloader. Select "Export & Launch SDK".

9. Create new application project selecting the option pointed:

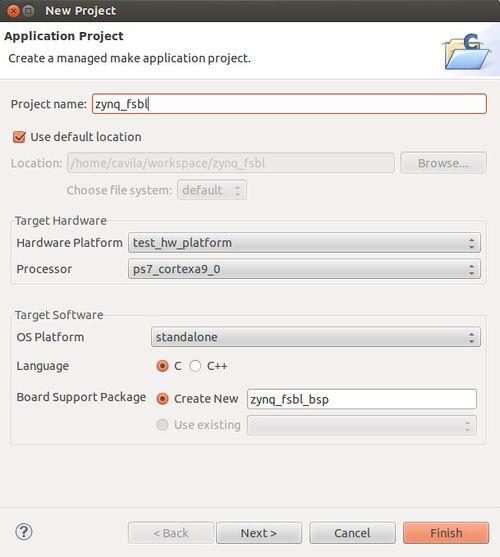

10. Name the application "zynq_fsbl" as shown, this step is required for the RidgeRun SDK, who will look for a file with this name. Then click on next option.

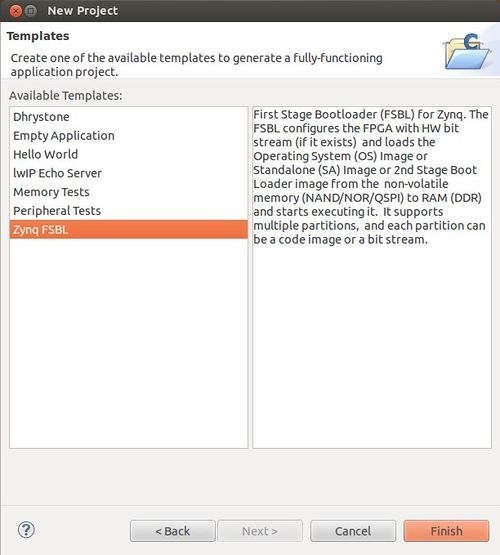

11. Select the "Zynq FSBL" template and click finish.

12. After all this steps you should have a bitstream (system.bit) and a first stage bootloader (zynq_fsbl.elf) inside the workspace you select for the Xilinx SDK. Just make sure that is for the project you were working on.