Difference between revisions of "V4L2 FPGA"

m |

|||

| (42 intermediate revisions by 5 users not shown) | |||

| Line 1: | Line 1: | ||

| − | <seo title="V4L2 | + | <seo title="V4L2 FPGA | V4L2 FPGA Driver | RidgeRun" titlemode="replace" metakeywords="v4l2, gstreamer acceleration, pcie, hardware acceleration, FPGA, GStreamer, v4l2 fpga, v4l2 driver, hardware accelerator, fpga ISP, Image Signal Processor, fpga driver, NXP, NVIDIA, i.MX8, Jetson, NVIDIA Jetson, TX1, TX2, Xavier, NVIDIA Xavier, Xilinx, Xilinx Ultrascale, Ultrascale ZCU106, Ultrascale+, PCIe interface, OPENCV" metadescription="V4L2 FPGA is V4L2 driver which can read and write to a hardware accelerator connected through a PCIe interface."></seo> |

| − | {{DISPLAYTITLE:V4L2 | + | {{DISPLAYTITLE: V4L2 FPGA Driver|noerror}} |

| − | {| style="border-style: solid; border-width: 1px; margin: | + | <noinclude> |

| + | {{V4L2_FPGA/Foot||Introduction}} | ||

| + | </noinclude> | ||

| + | |||

| + | {| style="border-style: solid; border-width: 1px; margin: 9px;" | ||

|- | |- | ||

| width="100%" valign="center" | | | width="100%" valign="center" | | ||

| − | <div style="padding: | + | <div style="padding:1rem 1rem; margin:0; background-color:#4db6ac;color:#ffffff;"> |

<div> | <div> | ||

| − | <p style="font-size: | + | <p style="font-size: 3.73em; margin-bottom:0">Welcome to V4L2 FPGA Drivers</p> |

| − | <p style="font-size: 1em; margin-top:0; margin-bottom:4rem">A V4L2 | + | <p style="font-size: 1em; margin-top:0; margin-bottom:4rem">A V4L2 FPGA driver for hardware accelerators.</p> |

</div> | </div> | ||

</div> | </div> | ||

| − | | rowspan=" | + | | valign="center" style="text-align:center;" | |

| + | [[File:Ultrascale_ZCU106.jpg|200px|Utrascale+]] | ||

| + | | rowspan="3" valign="top" style="text-align:center;" | {{V4L2_FPGA/TOC}} | ||

| + | |- | ||

| + | | width="100%" valign="top" colspan="2" style="background-color: #4db6ac; font-weight: bold; text-align: center; color:#ffffff"| | ||

| + | V4L2 FPGA - v0.9.0 | ||

|- | |- | ||

| − | | width="100%" valign="top" | | + | | width="100%" valign="top" colspan="2"| |

| − | |||

| − | |||

| + | [https://www.ridgerun.com/ RidgeRun] knows how critical it is to get the most of your hardware and optimize your system processing. On this matter, [https://www.ridgerun.com/fpga-development FPGA] acceleration is becoming one of the most used acceleration techniques in servers and embedded systems, going from simple high-speed frame grabbers to more complex image processing accelerators. | ||

| + | <br><br> | ||

| + | <center> | ||

| + | <embedvideo service="youtube">https://youtu.be/QnOHaGuC76c</embedvideo> | ||

| + | </center> | ||

| + | <br> | ||

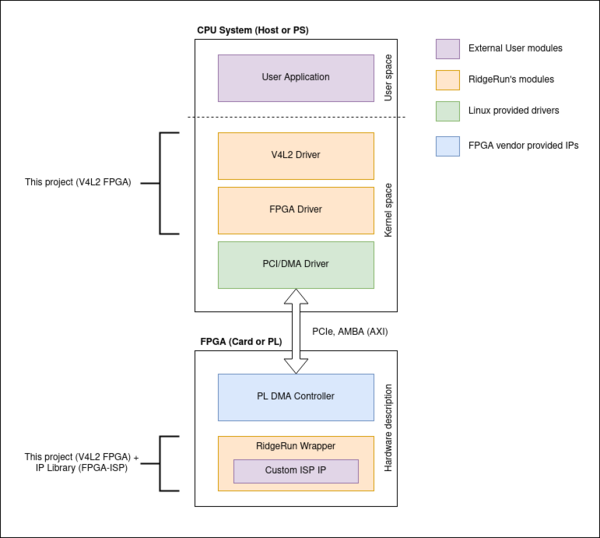

| + | Interfacing FPGA accelerators with commercial SoCs is usually a hard task and sending or retrieving data from the FPGA usually becomes a custom, non-standard communication design that leads to scalability problems. With this in mind, RidgeRun has developed the V4L2-FPGA driver as an alternative to solve FPGA-SoC communication in a more standard way, without sacrificing communication performance and make you able to concentrate on the FPGA hardware description. V4L2-FPGA driver allows communicating with an external FPGA using the V4L2 API. Thus, the interaction FPGA-System is achieved over a video device that provides or consumes video frames. It makes it easier to integrate your FPGA accelerators with V4L2 compliant frameworks such as GStreamer and get access to the hardware acceleration, providing a great option to add extra processing power to platforms such as i.MX8 and the NVIDIA® Jetson™ family. V4L2 FPGA supports FPGAs connected to CPUs through PCIe and AMBA (AXI). | ||

| + | Additionally, this project provides both drivers and wrappers to adapt your current Image Signal Processing IPs to a V4L2 compliant device. You may be also interested in our ISP library: [[FPGA Image Signal Processor|FPGA ISP]]. | ||

| + | <br><br> | ||

| + | [[File:V4l2 fpga sw stack.png|thumb|center|600px|Figure 1. Software stack description using V4L2 FPGA]] | ||

| + | <br> | ||

| + | |- | ||

| + | | width="100%" valign="top" colspan="3" style="background-color: #63a3ff; font-weight: bold; text-align: center; color:#ffffff"| | ||

| + | RidgeRun support | ||

| + | |- | ||

| + | | width="100%" valign="top" colspan="3"| | ||

| + | Get started with V4L2 FPGA Driver by clicking the button below! <br> <br> | ||

| + | <br> | ||

| + | [[File:xavier_get_started_here.png|400px|frameless|center|link=V4L2_FPGA/Introduction]] | ||

| + | <br> | ||

| + | <center> | ||

| + | <table> | ||

| + | <tr> | ||

| + | <td> | ||

| + | {{Shopping_cart_mpo}} | ||

| + | <td> | ||

| + | </tr> | ||

| + | </table> | ||

| + | <center> | ||

| − | + | <br> | |

| − | + | {{ContactUs}} | |

<center> | <center> | ||

{{Sponsor Button}} | {{Sponsor Button}} | ||

| − | <center> | + | </center> |

| − | |||

| − | |||

|} | |} | ||

| − | |||

<noinclude> | <noinclude> | ||

| − | {{ | + | {{V4L2_FPGA/Foot||Introduction}} |

</noinclude> | </noinclude> | ||

Latest revision as of 15:04, 17 May 2023

|

Welcome to V4L2 FPGA Drivers A V4L2 FPGA driver for hardware accelerators. |

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

V4L2 FPGA - v0.9.0 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

RidgeRun knows how critical it is to get the most of your hardware and optimize your system processing. On this matter, FPGA acceleration is becoming one of the most used acceleration techniques in servers and embedded systems, going from simple high-speed frame grabbers to more complex image processing accelerators.

Additionally, this project provides both drivers and wrappers to adapt your current Image Signal Processing IPs to a V4L2 compliant device. You may be also interested in our ISP library: FPGA ISP.

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

RidgeRun support | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Get started with V4L2 FPGA Driver by clicking the button below! Error creating thumbnail: Unable to save thumbnail to destination

Error creating thumbnail: Unable to save thumbnail to destination

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||